Intel เริ่มเดินเครื่องผลิตชิปเทคโนโลยี High-NA EUV ที่ Fab 52 แล้ว ถือเป็นเครื่องผลิตชิปที่ทันสมัยที่สุดในเวลานี้

อินเทลเดินหน้ารุกหนักทั้งด้านเทคโนโลยีการผลิตและการขยายโรงงาน ล่าสุดเริ่มใช้งานเครื่องฉายแสง High-NA EUV เชิงพาณิชย์เครื่องแรกของโลกที่โรงงาน Fab 52 ในสหรัฐฯ พร้อมเดินหน้าโหนด 18A เข้าสู่การผลิตปริมาณมาก และเตรียมขยายแคมปัสในซานตาคลาราเพิ่มเติม

Intel เดินเครื่อง High-NA EUV ที่ Fab 52

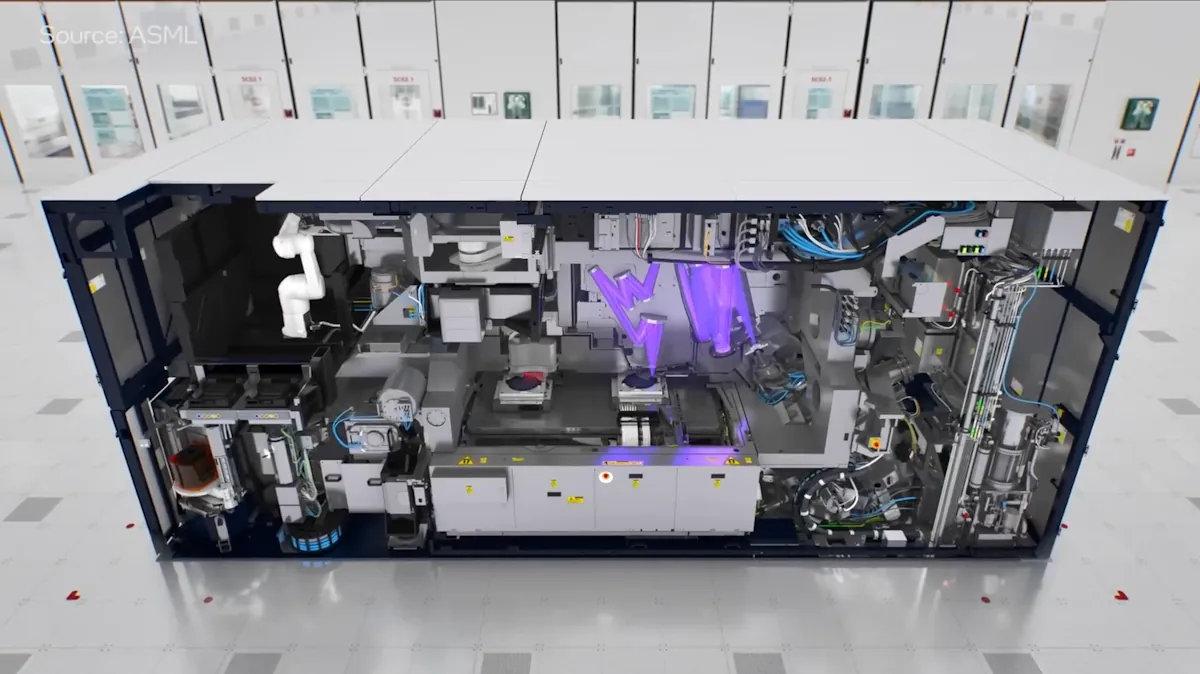

อินเทลได้นำระบบฉายแสง ASML Twinscan EXE:5200B ซึ่งเป็นเครื่อง High-NA EUV เชิงพาณิชย์เครื่องแรกของโลกเข้ามาติดตั้งและเดินเครื่องที่โรงงาน Fab 52 เมืองแชนด์เลอร์ รัฐแอริโซนา ด้วยมูลค่าลงทุนราว 380 ล้านดอลลาร์สหรัฐ จุดเด่นของเทคโนโลยีนี้คือการเพิ่มค่า numerical aperture จาก 0.33 เป็น 0.55 ทำให้ความละเอียดลายวงจรจากเดิมระดับ 13.5 นาโนเมตรลดลงได้ถึงราว 8 นาโนเมตร และลดความจำเป็นของกระบวนการ multi-patterning ที่ซับซ้อนลงอย่างมาก

ระบบ High-NA ที่ Fab 52 สามารถรองรับอัตราผลิตได้ประมาณ 175 แผ่นเวเฟอร์ต่อชั่วโมง พร้อมความแม่นยำด้าน overlay อยู่ที่ระดับ 0.7 นาโนเมตร ซึ่งถือเป็นระดับที่ตอบโจทย์การผลิตโหนดขั้นสูงในอนาคต อินเทลวางแผนใช้เทคโนโลยีนี้กับโหนด 14A (ระดับ 1.4nm-class) ซึ่งคาดว่าจะให้ประสิทธิภาพต่อวัตต์ดีขึ้นอีกราว 15–20% เมื่อเทียบกับโหนด 18A ที่ใช้อยู่ในปัจจุบัน

ปิดดีล “5 โหนดใน 4 ปี” กับ 18A และ Panther Lake

ควบคู่กับ High-NA อินเทลประกาศว่าโหนด 18A (ระดับ 1.8nm-class) ได้เข้าสู่การผลิตปริมาณมากเรียบร้อยแล้วในเดือนธันวาคม 2025 ถือเป็นหมุดหมายสำคัญของแผน “5 nodes in 4 years” ภายใต้นโยบายของซีอีโอคนก่อนและต่อเนื่องมาถึงซีอีโอใหม่ โหนด 18A จะถูกใช้ในซีพียูตระกูล Core Ultra 300 โค้ดเนม Panther Lake ที่เตรียมเปิดตัวอย่างเป็นทางการในงาน CES 2026 วันที่ 5 มกราคมนี้

Panther Lake จึงกลายเป็นแพลตฟอร์มสำคัญที่สะท้อนทั้งการฟื้นตัวและการกลับมาทวงความเป็นผู้นำด้านกระบวนการผลิตของอินเทลในตลาดพีซีระดับพรีเมียม เมื่อจับคู่กับการผลักดัน High-NA สำหรับโหนดถัดไปอย่าง 14A ก็ยิ่งตอกย้ำกลยุทธ์ “ไล่แซง” คู่แข่งด้วยการกระโดดเข้าสู่เทคโนโลยีล้ำหน้าก่อนใคร

แผนขยายโรงงานที่ซานตาคลารา

ในฝั่งซิลิคอนแวลลีย์ อินเทลได้ยื่นขออนุมัติขยายพื้นที่แคมปัส Bowers ในเมืองซานตาคลารา โดยมีแผนก่อสร้างอาคารผลิต 3 ชั้น พร้อมอาคารสาธารณูปโภค ติดกันรวมพื้นที่ใช้สอยราว 107,000 ตารางฟุต บนที่ดินประมาณ 2.4 เอเคอร์บริเวณมุมตะวันตกเฉียงใต้ของแคมปัสที่อินเทลใช้มาตั้งแต่ทศวรรษ 1970 อาคารสาธารณูปโภคจะรองรับระบบทำความร้อน การทำความเย็น และระบบไฟฟ้า เพื่อสนับสนุนการเดินเครื่องของโรงงานผลิตแห่งใหม่

โครงการนี้คาดว่าจะผ่านการพิจารณาในที่ประชุมเมืองช่วงต้นปี 2026 หากได้รับไฟเขียว เป้าหมายคือเริ่มก่อสร้างช่วงกลางปี 2026 และใช้เวลาก่อสร้างประมาณ 1 ปี การลงทุนดังกล่าวสะท้อนว่าบทบาทของซานตาคลารายังคงเป็นหนึ่งในศูนย์กลางการดำเนินงานด้านวิศวกรรมและการผลิตของอินเทลควบคู่ไปกับแผนขยายโรงงานในรัฐอื่นของสหรัฐฯ

เกมชิงความเป็นผู้นำกับ TSMC

การเลือกเดินหน้าใช้ High-NA EUV ก่อน ถูกมองว่าเป็นทางเดินที่ต่างจาก TSMC คู่แข่งหลักที่ยังไม่รีบผนวก High-NA เข้ากับสายการผลิตจริง โดยคาดว่า TSMC จะเริ่มใช้เทคโนโลยีนี้กับโหนดถัดไปในช่วงปี 2027–2028 ปัจจุบัน TSMC ได้เริ่มผลิตปริมาณมากที่โหนด 2nm ด้วยเทคโนโลยี EUV แบบมาตรฐานแล้วตั้งแต่ไตรมาส 4 ปี 2025

สำหรับอินเทล การนำ High-NA มาใช้กับโหนด 14A ช่วยให้ลดชั้นกระบวนการและผลักความละเอียดของลายวงจรให้ล้ำหน้ากว่าโหนด 2nm ที่ยังใช้ EUV แบบเดิม ซึ่งหากทำได้ตามแผนอาจพลิกตำแหน่งกลับมาเป็นผู้นำด้านกระบวนการผลิตในเชิงเทคนิคอีกครั้ง ในมุมมองเชิงธุรกิจ เทคโนโลยีนี้ยังเป็นจุดขายสำคัญต่อดีล Intel Foundry Services ที่ต้องการดึงลูกค้ารายใหญ่ให้หันมาเทผลิตชิปกับอินเทลมากขึ้น

มองภาพรวมยุทธศาสตร์ของ Intel

เมื่อมองภาพรวม การเดินเครื่อง High-NA ที่ Fab 52 การปิดดีลโหนด 18A เข้าสู่การผลิตจริง และการขยายโรงงานที่ซานตาคลารา ล้วนเชื่อมโยงกันเป็นกลยุทธ์ระยะยาวเพื่อดันอินเทลกลับสู่แถวหน้าของอุตสาหกรรมเซมิคอนดักเตอร์ อินเทลกำลังพยายามผสานจุดแข็งด้านเทคโนโลยีกระบวนการผลิตกับการลงทุนด้านโครงสร้างพื้นฐานโรงงานในสหรัฐฯ เพื่อสร้าง ecosystem การผลิตครบวงจรที่แข่งขันได้ทั้งกับ TSMC และซัมซุง

สำหรับสายฮาร์ดแวร์ พีซี และเซิร์ฟเวอร์ การมาของ Panther Lake (18A) และโหนด 14A ในยุค High-NA จะเป็นจุดเปลี่ยนสำคัญที่ควรจับตาทั้งในแง่ประสิทธิภาพต่อวัตต์ การกินไฟ และต้นทุนการผลิตของซีพียูและชิปยุคถัดไป

You must be logged in to post a comment.